#### ULTRASONIC PHASED-ARRAY DRIVER SYSTEM

#### BY

#### FRANCIS CHINH NGO

B.S., University of Illinois, 1988

#### **THESIS**

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 1989

Urbana, Illinois

### UNIVERSITY OF ILLINOIS AT URBANA-CHAMPAIGN

#### THE GRADUATE COLLEGE

|                                   | AUGUST 1989                               |

|-----------------------------------|-------------------------------------------|

|                                   |                                           |

|                                   | •                                         |

| WE HEREBY RECO                    | OMMEND THAT THE THESIS BY                 |

|                                   | FRANCIS CHINH NGO                         |

| ENTITLED ULTRA                    | ASONIC PHASED-ARRAY DRIVER SYSTEM         |

| BE ACCEPTED IN PAI                | RTIAL FULFILLMENT OF THE REQUIREMENTS FOR |

| THE DEGREE OF                     | MASTER OF SCIENCE                         |

|                                   | Charles a Can                             |

|                                   | Director of Thesis Research               |

|                                   | Simothy M. Suid Head of Department        |

|                                   | · ·                                       |

| Committee on Final Examir         | nation†                                   |

|                                   | Chairperson                               |

|                                   | Chair person                              |

|                                   |                                           |

|                                   |                                           |

|                                   |                                           |

| † Required for doctor's degree b  |                                           |

| i recommend for doctor's degree t | out not for master 5.                     |

O-517

## UNIVERSITY OF ILLINOIS AT URBANA-CHAMPAIGN GRADUATE COLLEGE DEPARTMENTAL FORMAT APPROVAL

| THIS IS TO CERTIFY THAT THE FORMAT AND QUALITY OF PRESENTAT | ION OF THE THESIS  |

|-------------------------------------------------------------|--------------------|

| SUBMITTED BY FRANCIS CHINH NGO                              | AS ONE OF THE      |

| REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE            |                    |

| IS ACCEPTABLE TO THE DEPARTMENT OF ELECTRICAL AND COMPUTER  |                    |

| Full Name of Department, Division or U                      | Init               |

| 26 July 1000                                                | IK.A.              |

| 26 July 1989 / Like                                         | 11XV               |

| Date of Approval                                            | tal Representative |

#### **ACKNOWLEDGEMENTS**

The author would like to express his deep gratitude to Professor Charles A. Cain for the opportunity to conduct this thesis project. His guidance, encouragement, and patience have helped the author through many problems. He would also like to thank Emad S. Ebbini, Mohammed Ibbini, and Dr. Shin-Ichiro Umemura for their criticisms and helpful discussions.

The Ultrasonic Phasd-Array Driver System was the product of the thoughts and efforts of many people. Recognition should be given to Dr. Shin-Ichiro Umemura and Professor Charles A. Cain for their development of the RF amplifier, Emad S. Ebbini for his design of the digital control circuits, and to Fred Heyman for his development of the software. The author would like to extend sincere thanks to Patricia Dallmier, Jerry Valerio, and Andrew Dillon for their help in constructing the system. Their suggestions and contributions have helped the system evolve from the initial circuit layouts to a laboratory prototype.

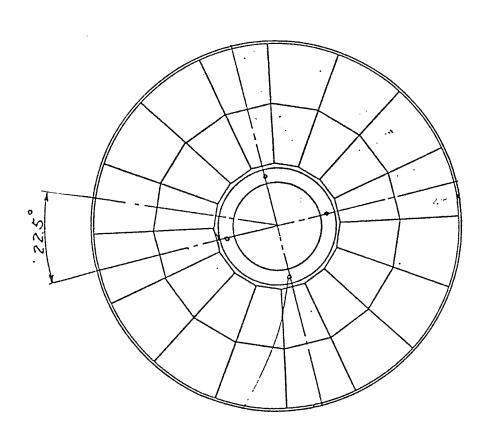

The Sector Vortex Array was designed by Professor Charles A. Cain and Dr. Shin-Ichiro Umemura. The author would like to extend his appreciation to them for allowing the array to be used in his research. He would also like to acknowledge Bill McNeill and Scott Sprague for their many innovations during their construction of the array. Appreciation is extended to Eric Schmidt and Patrick Patterson for the development of software used to evaluate the Sector Vortex Array.

The author would like to offer his thanks to the people who assisted in the preparation of this thesis: Wanda Elliott, Penny Shonkwiler, Marilyn Chen, Shary Chen, Patricia Dallmier, Eric Schmidt, Patrick Patterson, and Akila Srinivasan.

Finally, the author would like to extend his sincere appreciation to his friends, Shary Chen and Ellen Cheng, and especially Marilyn Chen for their love, unlimited support, encouragement, and advice.

This thesis is dedicated to the author's parents, for their continued support in his endeavors.

### TABLE OF CONTENTS

| CHAPTER |                            | PAGE |

|---------|----------------------------|------|

| 1       | INTRODUCTION               | 1    |

| 2       | SYSTEM OVERVIEW            | 4    |

| 3       | DIGITAL CONTROL CIRCUITS   | 8    |

| 4       | AMPLIFIER CIRCUITS         | 29   |

| 5       | SYSTEM BUSES               | 49   |

| 6       | SECTOR VORTEX PHASED-ARRAY | 61   |

| 7       | MATCHING CIRCUITS          | 70   |

| 8       | CONCLUSIONS                | 85   |

|         | REFERENCES                 | 109  |

## CHAPTER 1 INTRODUCTION

Cancer is one of the most prominent causes of illness related death in the world today. With already 3000 known carcinogens, it is a problem that requires due attention. However, most attempts for finding a cure have met with very limited success. One of the main reasons stems from the difficulty in targeting a therapy at a cancerous tumor without affecting the vital cells situated nearby.

Hyperthermia may be able to sustain preferential killing of the cancerous tissue by exploiting a tumor's sensitivity to heat caused by its environmental conditions. For example, blood flow is often the sole means of heat removal from the tumor area. However, blood flow rates in tumors tend to be 0.4 times less than that in normal tissue [1]. Furthermore, some tumors lack the normal homeostatic response that causes an increase in blood flow with an increase in temperature; this aids heat conduction away from the area [2]. Other conditions which can sensitize the tumor to heat are nutrient depletion and an acidic environment.

One of the main problems associated with current hyperthermia treatments has been the inability to deliver the necessary heat to tumors without any unacceptable heating of the normal tissue. According to Samulski, the main reason that hyperthermia has failed to live up to its promise shown in previous biological experiments is "the technical difficulty of elevating tumors to appropriate temperatures and determining the

temperature distributions obtained. . . there is an insufficient effort in developing appropriate equipment [3]."

One device that holds great promise in this area of controlled heating in several superficial and deep lesions is the ultrasound phased-array. Taking advantage of the short wavelengths that can be used with ultrasound, phased-arrays allow focusing characteristics that are unparalleled in other current, noninvasive modalities. There are several other advantages offered by phasedarrays. First, microprocessor controlled phased-arrays have excellent control of their focus and can allow excellent localized heating patterns by steering their beam around a tumor's periphery. This microprocessor control is especially beneficial if the acoustic window or the tumor has a complex or asymmetric shape and requires easy modification of the scanning pattern. In cases where the tumor is confined to scattered areas or deep-seated volumes, there is often no other practical alternative to ultrasound phasedarrays for hyperthermia treatment. Often it is these deep-seated tumors which are the most life threatening [4]. This can be compounded with complications in the surgical removal of the tumor due to its inaccessibility. It is in cases such as this where noninvasive hyperthermia is the most advantageous.

Recent technological advances have renewed interest in localized hyperthermia. Noninvasive imaging, such as positron emission tomography may be used to investigate the blood flow in various areas. This gives an improved thermal mapping of the tumor vicinity and will allow hyperthermia to be used to its full capability. Utilizing phased-arrays, treatments can be administered

with less occurrence of undesirable cold spots which are often attributed to treatment failure.

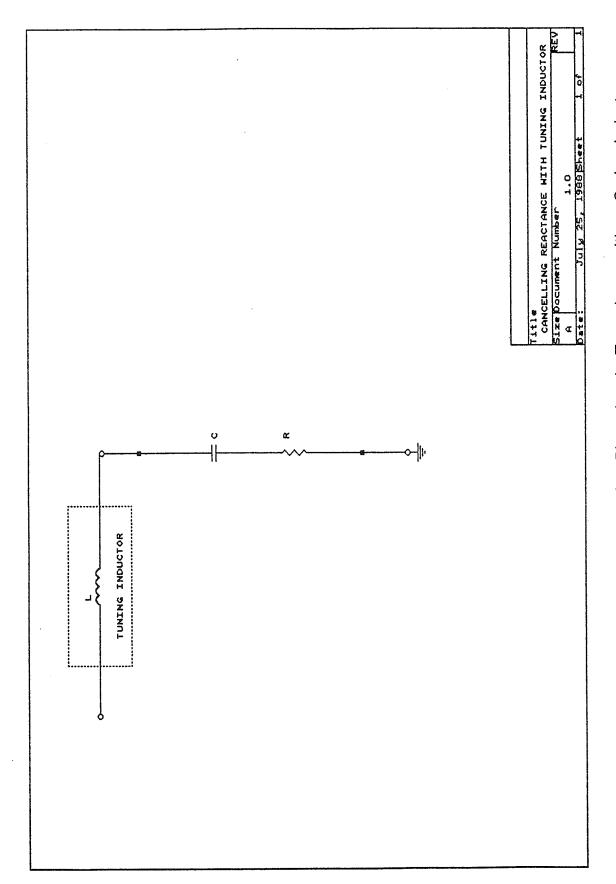

There are several potential problems with phased-arrays. The large number of elements in phased-arrays require a significant number of amplifiers. These amplifiers require a complicated controller that should allow the scanning patterns to be readily changed to suit the treatment conditions. Also, electrical coupling between the driving signals of the elements will become prominent at high frequencies largely due to the capacitive reactance of the transducers [5]. The primary objective of this thesis research is directed toward the solution of these problems in the process of designing and implementing an ultrasound phased-array driver system.

## CHAPTER 2 SYSTEM OVERVIEW

#### 2.1 Design Objective

The main objective of the Ultrasonic Phased Array Driver System (UPADS) is to generate the desired excitation signals for all of the elements in a phased array. As a laboratory prototype, the system should be extremely versatile so that it may be used with several different applicators. Finally, although the large number of elements demands a significant amount of hardware, much of it is redundant so that the system should be designed with easily reproducible components.

### 2.2 Design Specifications

There are certain specifications that become evident from the design objective. First, consider the requirements for driving different applicators:

- Since each applicator may have a unique resonance frequency, the driving system must allow various operating frequencies.

- 2. Since the applicators may have different efficiencies, the system should have an adjustable power output.

- 3. Since each array may have a different number of elements, the number of active drivers should be controllable.

4. Because each element will require a specific matching network depending on the array, the system should allow interchangeability of these circuits.

Second, in order to facilitate analysis of different phasing techniques,

- 1. The system should simultaneously output all of the signals to the phased array.

- The transition time between focal points should be minimized.

- 3. The system should always be accessible for emergency shutdown.

- 4. There should be an easy means of loading data into the system since its record size is large.

Finally, in order to facilitate the realization of the system,

- 1. The system should be subdivided into modules according to their functions to simplify system repair and debugging.

- 2. All of the modules should share a general form for simple reproduction since there is some redundancy in the system.

- 3. The system should be expandable so that arrays with more than 64 elements can also be driven.

## 2.3 System Description

UPADS consists of 5 major components. They are,

- 1. User Interface

- 2. System Bus

- 3. Digital Control Circuits

- 4. Amplifier Circuits

- 4. Matching Circuits

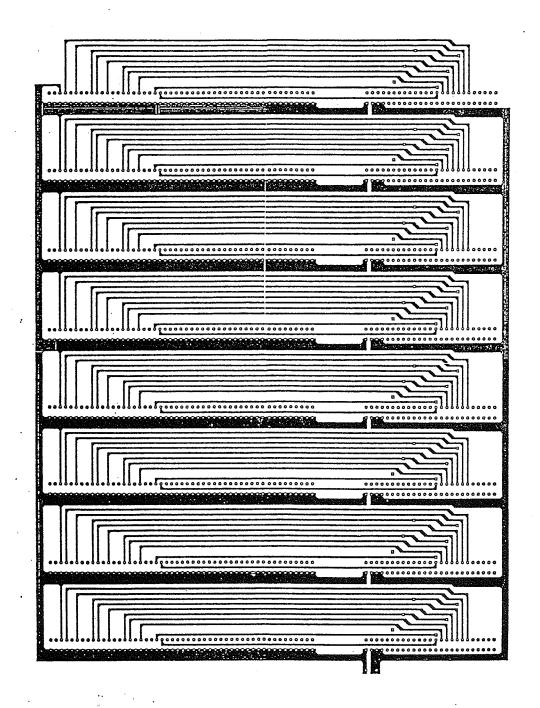

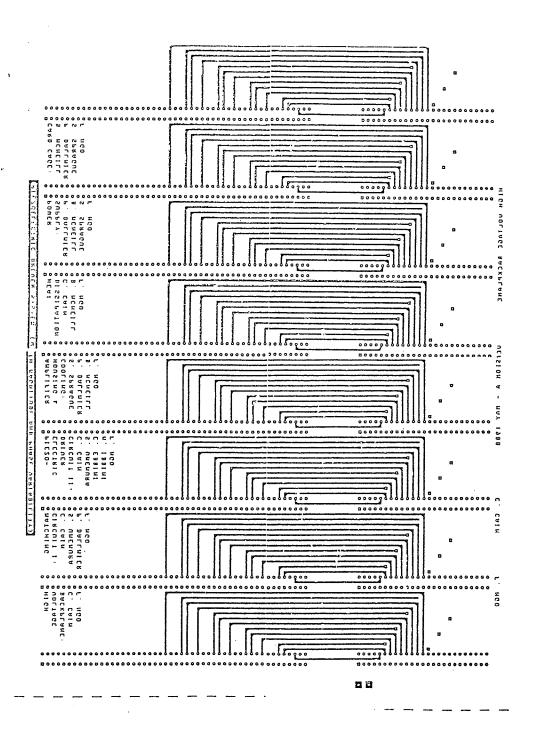

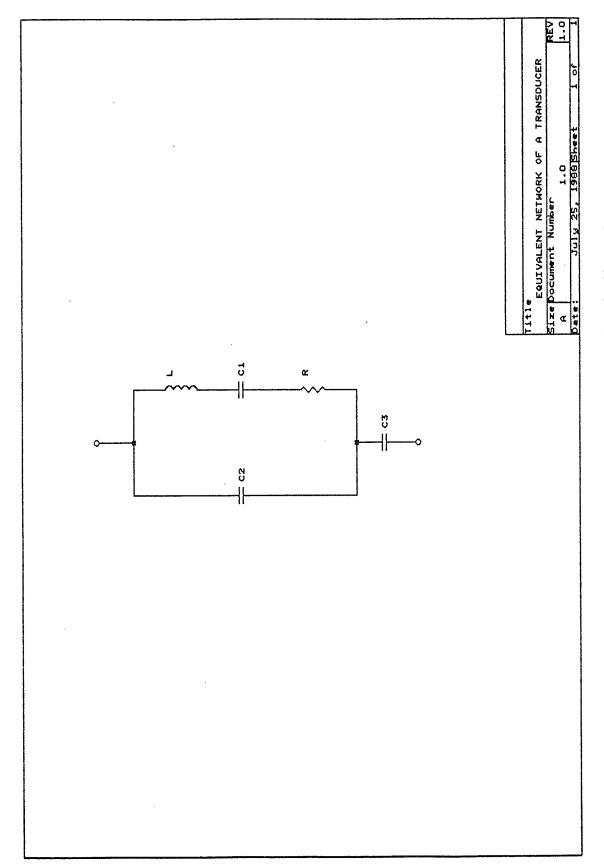

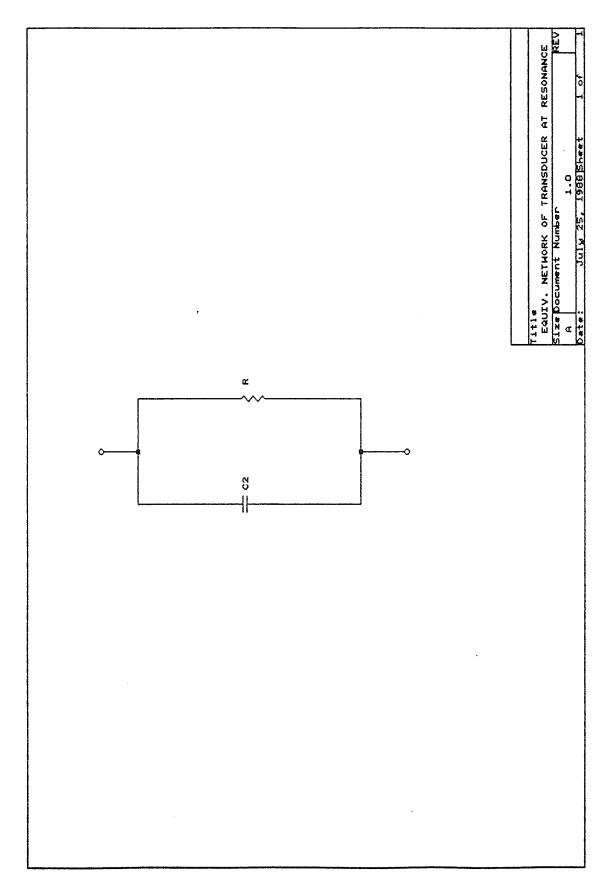

The user interface allows the user to enter the desired amplitude and phase of each element's driving signal on a personal computer (PC). This can be done via keyboard entry or flat ASCII file on a floppy disk. Once the PC has processed and converted the data to binary, the data will be outputted by a Direct Memory Access (DMA) card onto the system bus, which delivers the data to the Digital Control Circuits (DCC). The main role of the DCC is selecting the specified data for each element from the system bus, converting it to a square waveform with the desired duty cycle and phase, and inputting the waveform into the amplifier circuits. It is the amplifier circuits' responsibility to increase the voltage to a level suitable for driving the piezoelectric transducer elements. signals are then sent from the output of each amplifier through a separate component of the system bus to its corresponding matching network, which is utilized to cancel the reactance of the transducer element so that the amplifier can drive a resistive load.

#### 2.4 Practical Considerations

A prototype system with 64 channels was constructed to the specifications mentioned above. Due to space limitations and for reasons that will become clear later, the drivers were divided into modules with only 8 channels. Accordingly, the matching networks were grouped in modules of 8 and connected to the amplifiers by an in-house bus. The module concept is helpful in

repairing the system. Because each module is identical, if an amplifier module is not operating correctly, it can be easily replaced with another one. Also, it facilitates system debugging by allowing it to be done on both the system and module levels. These modules were designed and laid out on printed circuit boards (PCB). This allowed the circuits to be easily reproduced, made the system more reliable, and minimized differences in response between channels.

# CHAPTER 3 DIGITAL CONTROL CIRCUITS

#### 3.1 Design Objective

As was noted in the Introduction, the implementation of 64 square waves with specified amplitudes and phases is crucial to the operation of a phased array. This is accomplished by the Digital Control Circuits (DCC) outputting to MOSFET amplifiers (discussed in Chapter 4), which elevate the signals to a level capable of driving the individual elements in the array. Note that although most of the numerical conversion takes place in the personal computer (PC), the actual waveforms are generated by the DCC.

### 3.2 Design Specifications

The DCC has several design specifications which are necessary to satisfy the design objective

- In order to preserve the phase information, the DCC should have a parallel output to all of the elements for a specific focal pattern. A sequential output of the waveforms will have an inherent phase error due to the relative time delay.

- 2. The DCC must be accessible by the DMA to either output another focus or shut down the system.

- 3. If the scanning method is used to acquire the desired heating pattern, and the dwell time for each focal point is used to compensate for intensity loss, the time averaged intensity of the scanned field can be given by Equation (3.1):

$$I_{av}(x, y, z) = \frac{1}{T_s} \sum_{l=1}^{N_f} I_l(x, y, z) \Delta T_l$$

(3.1)

where  $T_s$  is the scan period,  $N_f$  is the number of focal points,  $I_l$  (x, y, z) is the field intensity profile of the lth focal point and  $\Delta T_l$  is the dwell time at that point [6]. In order to maintain the maximum possible dwell time at each focal point, the DCC should continue to generate waveforms up to the output of the next focal point.

These features will be discussed throughout this chapter.

#### 3.3 Circuit Description

#### 3.3.1 Variable amplitude phase shifting network

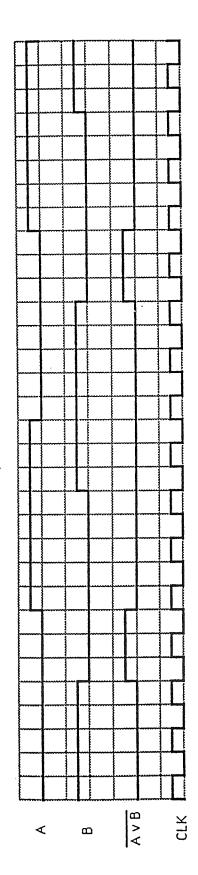

The central component of the DCC is the Variable Amplitude Phase Shifting Network (VAPSN). The remaining circuitry is to control the VAPSN and to synchronize the DMA. The VAPSN consists of 64 clusters of two 74LS193 synchronous up/down four bit counters and a 7402 dual input NOR gate allowing each cluster to independently synthesize a waveform. See Figure 3.1. (All figures appear after Chapter 8.) Only the most significant bit (MSB) output, QD, of each counter is used. When the system clock is connected to the count-up input of the counter, the MSB output will be high for eight clock cycles and low for eight clock cycles. This constitutes a 50% duty cycle square wave with a period equal to sixteen clock periods. Thus, the operating frequency of the system can be given by fsystem = fclock/16.

The transistor-to-transistor logic synchronization (TTL SYNCH) output of a Hewlett-Packard (HP) 3325A waveform

synthesizer/function generator is used as the system clock. Thus, the system is extremely versatile in that it can drive phased arrays with different resonant frequencies. The outputs of both counters are sent to the dual input NOR gate that outputs a high only when both inputs are low. Thus, by controlling the duration of time when both counters are low, the system may implement square waves with desired duty cycles. Figure 3.2 shows how a square wave with an 18.75% duty cycle might be generated.

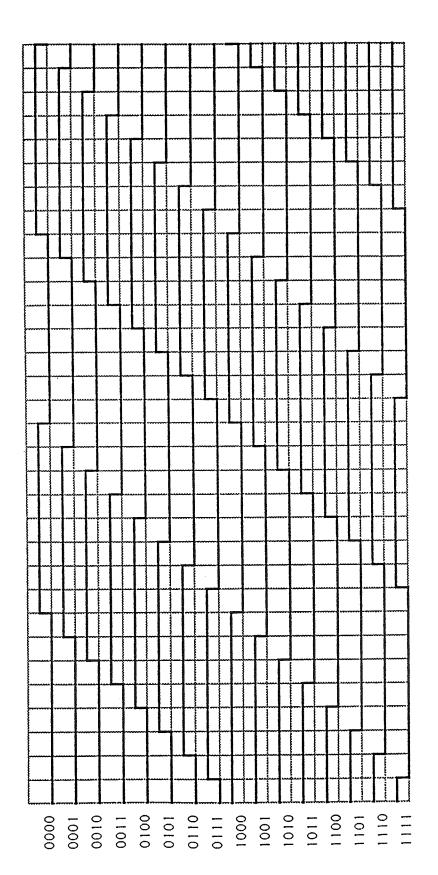

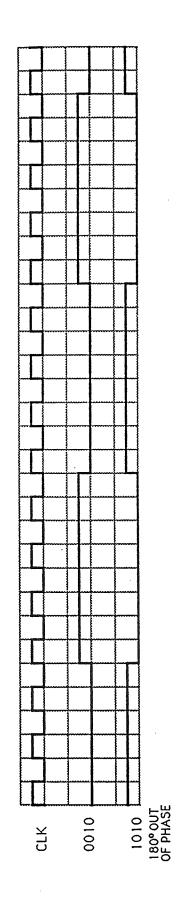

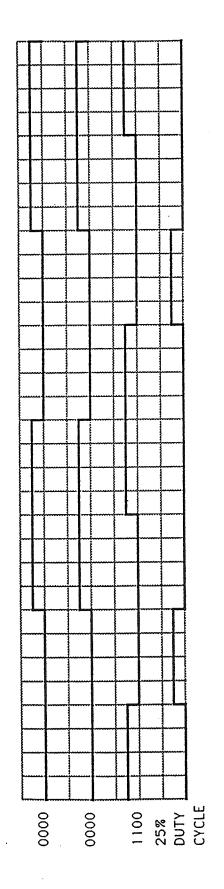

This control is implemented by programming each counter's preset inputs, which are used to set the initial state of the counter. Loading the presets causes a counter in the count-up mode to count from this initial state up to fifteen and then repeat the cycle of counting from zero to fifteen until the next load. Figure 3.3 shows the shifted outputs of a counter using different presets. Let the assigned reference signal be the output of the counter with a preset of 8 (1000 in binary). If the preset, P, of another counter is set between 0 and 8, the result is a 50% duty cycle square wave that lags the reference signal by (8 - P) x 22.5°. If the preset is between 9 and 15, the output will be the same square wave but leading the reference signal by (P - 8) x 22.5°. If the + and - notation is used to represent leading and lagging, respectively, then the phase is given by (P - 8) x 22.5°. Figure 3.4 displays how this phase shifting technique can be used to construct two waveforms that are 180° out of phase.

As was mentioned previously, the outputs of both counters in the cluster are sent to a NOR gate. The second counter is used to control the duty cycle. In order to control the duration that both

outputs are low, the second counter's preset must be set relative to the first counter's preset. Therefore, the first counter in the cluster is used to set the relative phase with respect to a reference signal while the second counter in the cluster is used to set the duty Both the phase and amplitude information are actually a function of the two presets. This is illustrated by Figure 3.5, which shows the presets needed to implement a waveform with a duty cycle of 25% and a phase shift of 135° with respect to a reference signal generated by a counter which was preset to 0. In addition, the maximum duty cycle of 50% is obtained by taking the NOR of two identical waveforms. A duty cycle of 43.75% can be achieved by taking the NOR of waveforms outputted by counters with presets that differ by one. Furthermore, an element can be inactivated by setting the presets so that they differ by eight. As a result, only one of the two counters will be low at any time, causing the NOR gate to always output a low signal.

It is readily apparent that only eight duty cycles can be achieved by this system. Thus, although 8 bits are necessary to specify a certain phase shift and duty cycle, there is, in actuality, only 3 bits of resolution for the duty cycle and 4 bits of resolution for the phase, as was shown by the 16 waveforms in Figure 3.3. Also, it should be noted that one waveform is necessary as a reference.

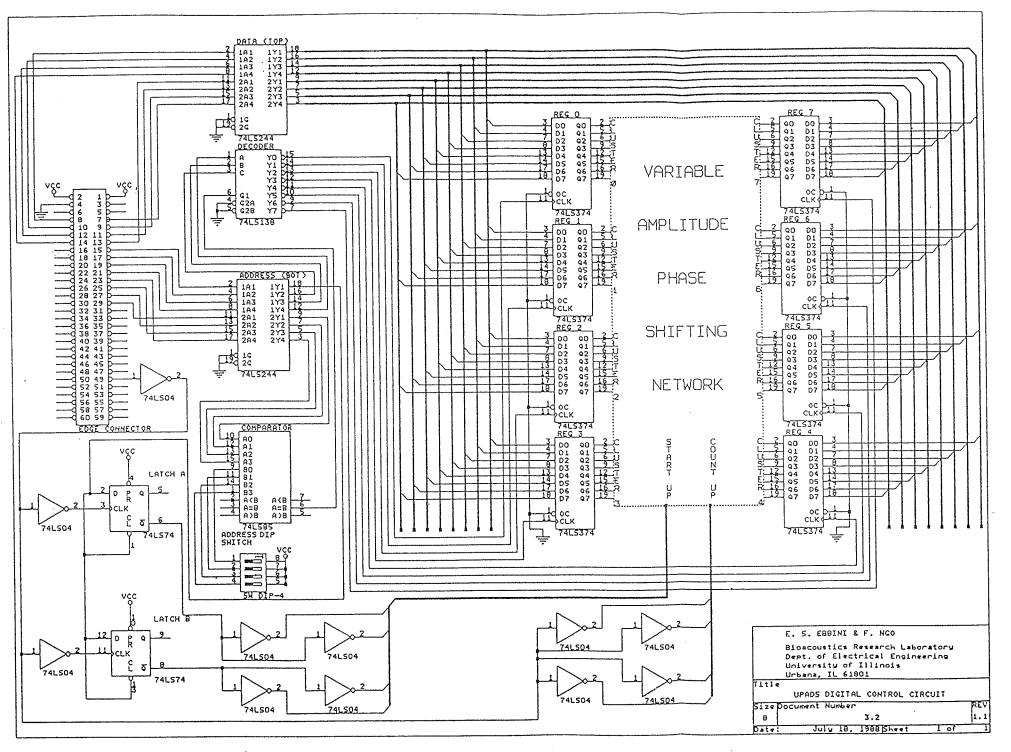

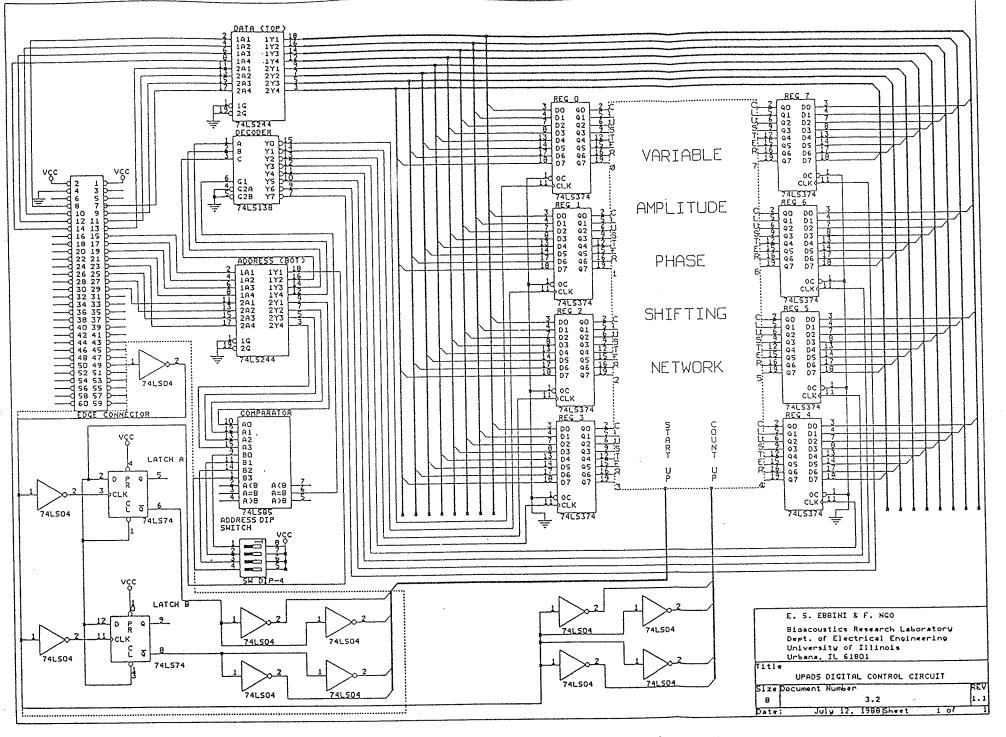

## 3.3.2 Variable amplitude phase shifting network control circuits

The Variable Amplitude Phase Shifting Network Control

Circuits (VAPSNCC) is responsible for gating the data from the DMA

into the presets of the counters. (See Figure 3.6.) The data for each

focal pattern consist of 64 eight bit words (four bits per counter).

In addition, addressing bits are necessary for data selection from

the bus. Because working with this data record was too

cumbersome, the data was broken into smaller packets, one per

cluster. Each packet contains one eight bit datum and a

corresponding eight bit address word for addressing the selected

cluster. These packets are outputted sequentially by the DMA onto

the STD bus. Thus, in order to generate all of the signals required

for a single focal pattern, the data for each cluster must be loaded

one at a time, beginning with cluster 0 and ending at cluster 63.

The stipulation that the DCC should simultaneously output all 64 waveforms necessitated the use of clocked storage for each cluster. Holding registers, implemented by 74LS374 Octal D-type Flip-Flops which require no complicated handshaking for loading, serve this function well. The data is downloaded from the DMA onto the bus. After a delay which allows the data to stabilize, the address word is inputted to the control circuits, which subsequently clock the corresponding register, causing it to take the state of its inputs. This process is then repeated until all of the remaining registers have been loaded. Note that the data at the D-type Flip-Flop outputs will remain latched at their present state until a register is clocked again. Because each of the registers' inputs are

placed on a common bus for all 64 clusters, the control circuits need to clock only the selected cluster register when its respective data is on the bus, so that the other 63 registers are in no danger of loading in the incorrect data.

The address word is comprised of four bits used for addressing a specific board in the system and the three bits used for selecting a particular cluster on a board. Thus, the system's configuration has a maximum of sixteen boards with eight clusters residing on each board. The board address is set via a four bit hexidecimal hybrid rotary dip switch and implemented by an on-board four bit magnitude comparator. The comparator, a 74LS85, compares the address set by the switch with the four bits in the address word allocated for board selection. In the event of a match, the comparator sends a logic level high signal to the A=B output, which is tied to the active high enable of a three to eight decoder (74LS138) of the selector board. Once enabled, the decoder outputs a logic level low signal to one of the eight clusters, which is selected using the three bits allocated for cluster selection. Each decoder output is tied to its respective register's clock. Thus, when a specific cluster's data comes on line, a comparator selects the correct board and enables a decoder which clocks the corresponding cluster's register, loading it with the specified data. The DMA then outputs the next cluster's data and the process repeats until the remaining registers have been loaded.

Since the outputs of each register are tied directly to the presets of the two counters in its respective cluster, to update the presets with the data stored in the register, the DMA needs only to

output a common logic level low load command in the address word (1 load bit) to all of the counters. (In order to avoid confusing this load with the load outputted by the addressing network to the registers, the former will be referred to as the startup command.) The startup command overrides the system clock and forces the counters' presets to take the state stored in the register. This is called a jam load. When the load signal goes high, the counter will count with every positive edge of the system clock. However, this load is asynchronous to the clock and thus can occur anywhere along the clock cycle. It is, therefore, possible that the load goes high at approximately the same instant as the count-up clock goes high. On this occasion, the required setup time for the enable input (removal of the load signal) will not be satisfied. The setup time is defined as the amount of time that an input is required to be stable before another event can occur. In this case, the removal of the load occurs too close to when the count-up signal is applied. According to its data sheets, the 74LS193 will operate in the guaranteed mode at clock speeds around 25 MHz. The minimum load inactive-state setup time, t<sub>SU</sub>, for the 74LS193 is approximately 15 ns. If the system clock is running at 12 MHz, this setup time corresponds to approximately one-fifth of a clock period. Thus, it is readily apparent that the load inactive-state setup time will not be met if the count-up goes high within 15 ns after the load has been removed. This event could create a metastable state; for the same clock input there are two possible counter outputs. The counter could either count up with the positive edge of the clock, or count up with the next positive edge.

Since the counters are not operating in the guaranteed mode, the output of two counters receiving the same input could be different. Thus, a counter that was preset for a one count difference with respect to another counter could have, in actuality, a zero or two count difference. In this application, this translates into either

- 1. A square wave with a duty cycle that is 6.25% shorter or longer in duration than the intended duty cycle.

- 2. A cluster output that is shifted 22.5° with respect to its intended phase.

Since the phase information is extremely important to the operation of phased arrays, this phase error could seriously degrade a synthesized focal pattern that is both asymmetric and complex [7]. There are two possible remedies to this problem

- 1. If the count-up input of the counter was gated, it could be held high during the load sequence. After the load becomes inactive, the count-up input will go low on the next negative edge of the clock. This would give the load-inactive state one-half of a clock period for setup time. This setup time should suffice if the system clock is 12 MHz or less.

- 2. The second solution uses almost the same scenario as the first one except that it gates the load signal. If the load signal is synchronized with the negative edge of the clock, it would give the load one-half of a clock period before the count-up signal (clock) goes high. Once again, this should give ample amount of time for the setup of the load-inactive state. The second solution gives the same result

as the first solution but is somewhat easier to realize.

Thus, this solution is implemented in the Load

Synchronization Circuit, LSC (enclosed in the dashed lines in Figure 3.7.)

Because the load for the 74LS193 counters is an active low signal, the load-inactive state occurs on the positive edge of this signal. The positive edge of the load must be synchronized to the negative edge of the system clock which feeds the count-up of the counter. This can easily be done using D-type flip-flops, and there are several advantages to using them. First, unlike RS flip-flops, the D-type flip-flops have direct inputs such as a reset and a clear which do not require a clock pulse. Second, the D-type flip-flops are edge-triggered unlike most standard JK flip-flops which are level-triggered. Level-clocked devices require complicated timing sequences to ensure that the input states do not change when the clock is gating data. Thus, JK flip-flops require additional combinational logic to strobe the data in correctly.

Hence, a D-type flip-flop such as the 74LS74 would be ideal for triggering a signal to a certain edge of the clock pulse. The only drawback is that the 74LS74 is a positive edge triggered device. This is overcome easily by inverting the clock pulse and feeding it into the clock of the 74LS74. Thus, although the 74LS74 is still triggering on the positive edge, it is in actuality triggering on the negative edge of the system clock. With the active low load signal fed into the input, D, of the D-type flip-flop, the output, Q, will go low on the negative edge of the system clock. It should be noted that the D input remains asynchronous to the clock. Thus, it is still

a possibility that the DMA load signal could go high at the same instant that the inverted clock goes high. In this case Q could either take the same state as the input on this positive edge or do so on the next clock pulse. Therefore, the output could be delayed by one clock pulse. However, this still will not cause a problem since the output of the flip-flop is common to all of the counters in the system and is synchronized to a negative edge of the clock. Therefore, all of the counters in the system will see the same signal and have adequate setup time. The only effect that this metastable state will have is a maximum delay of one clock period in the loading of the next subsequent focal pattern into the presets of the counters. With a clock frequency of 12 MHz, this delay is approximately 83 ns. For all practical purposes, this is almost negligible compared to the actual dwell time of the focal pattern.

The output of the D flip-flop is sent to all of the boards along the synchronized load bus using line drivers (74LS244) whose output is tied to the clear input of a 74LS74 on each board. When the onboard 74LS74 receives the low load signal at the clear input, it will output a logic level high signal from  $\overline{Q}$ . This output is then fed into four inverters that in turn drives the load inputs of the sixteen counters. The inverters are necessary to give the required logic level low signal and also to avoid exceeding the fanout limit of the D-type flip-flop.

The DMA may need to access the DCC to serve one of two functions. If the scanning method is being used for local heating, the DMA will need to access the DCC each time it outputs a focus. Since the DCC acts as a peripheral that is always in the listen mode,

to access the DCC, the DMA needs only to output the data onto the bus. With no other talkers on the bus other than the DMA, handshaking is unnecessary. As the only device that is in the listen mode on the bus, the DCC receives everything that is downloaded onto the bus. The VAPSNCC waits for the address and upon its arrival clocks whatever is present on the data bus. The 16-bit output of the DMA is set up so that the 8-bit data word goes out first and stabilizes before the 8-bit address word is sent out. The second function stipulated in the circuit specification of immediate shutdown can also be realized by sending a preprogrammed output of the 0% duty cycles. Note that this and any other output can be sent without causing the system to glitch because the LSC synchronizes all outputs and allots the proper set up time.

The requirement that the output of the DCC be continuous is satisfied because the counter only utilizes the presets for the first cycle of counting to set the initial phase shift of each cluster's output. Since the counter receives the new state of the presets only when the startup signal is present, the registers can be changed to load the next focal pattern without affecting the counter upon removal of the signal. The only time the counters stop is during the startup command. Since the duration of this command is relatively small with respect to the average time constants attributed to tissue, the output can be considered continuous.

#### 3.4 System Hardware

## 3.4.1 Variable amplitude phase shifting network

The hardware used to construct the VAPSN is listed below:

- 1. 16 74LS193 4-Bit, synchronous binary up/down counters.

- 2. 8 74LS02 Dual input NOR gates.

The 74LS193 offers a synchronous mode of operation with 4-bit parallel load presets. There are several inherent advantages to using synchronous counters as opposed to asynchronous (ripple) counters. In a synchronous counter, all stages are clocked simultaneously by the steering logic which causes the stage outputs to change coincidentally with each other. Asynchronous counters are somewhat slower because each stage (flip-flop) of the counter must be clocked by the output of the stage preceding it, which results in an accumulated propagation delay. Also, output current spikes are commonly associated with ripple counters.

## 3.4.2 Variable amplitude phase shifting network control circuits

In order to implement the VAPSNCC, the following hardware was used:

- 1. 2 74LS244 Octal tristate noninverting drivers.

- 2. 1 74LS138 3 to 8 line decoder.

- 3. 1 74LS85 4-Bit magnitude comparator.

- 4. 8 74LS374 Octal D-type flip-flops.

- 5. 5 74LS04 Inverters.

- 6. 1 Hexidecimal Hybrid Rotary Dip Switch.

The following is a list of the TTL IC's used to implement the LSC.

- 1. 2 74LS74 Dual D-type flip flop with preset and clear.

- 2. 6 74LS04 Inverters.

Low power Schottky (LS) TTL was used for all IC's in the DCC. It offers speed comparable to the standard 74 series TTL with considerably less power consumption. There is a tradeoff however: 74LS is more sensitive to ground level noise spikes than the standard 74 series.

#### 3.5 Practical Considerations and Future Recommendations

When implementing a logic design and interfacing TTL IC's, the main design considerations are the prevention and elimination of noise. There are several reasons for this. First of all, the fairly low output signal level and noise margin make the TTL IC's extremely sensitive to noise introduced from external sources, power supplies, and switching noise. Secondly, TTL IC's are inherently noisy. Finally, since an interface often shares a common ground with the digital circuits, noise from the interface may pose a problem to the operation of the TTL IC's.

Since output can typically be 2.4 V for a logic high and 0.4 V for logic low (nominally 3.5 V and 0 V,respectively) with threshold input voltages of 2.0 V (V<sub>IL</sub> maximum) and 0.8 V (V<sub>IH</sub> minimum). Therefore, the noise margin for either logic level signal is possibly 0.4 V, although gates normally have a noise margin on the order of 1 V [8]. Any input between V<sub>IL</sub> maximum and V<sub>IH</sub> minimum will produce an unpredictable output. Thus, it is possible that noise

introduced to one logic level signal could make it to appear as the other logic level signal. Since the noise related problems are often intermittent, finding solutions to them may be time consuming and difficult. One possible approach is to discover and eliminate the sources of noise.

The two major sources of noise in the UPADS are the TTL circuits and the CMOS amplifier circuits. The noise source of the TTL circuits can be found in their output stages. Transistor-totransistor logic employs a totem pole output stage, characterized by a pair of output transistors tied between the power supply rail and ground. Its operation is similar to a push-pull circuit. When the upper NPN transistor is biased, the output swings to the VCC and pushes (sources) current; when the lower NPN transistor is biased, the output swings to ground and pulls (sinks) current. While this output stage possesses distinct advantages over pull-up type output stages, it has a major disadvantage. As the output goes through a state transition, both transistors will be active for a short amount of time. This presents a low impedance pathway between VCC and ground which allows a large current to flow into the ground from the power supply rail. The end result is a current pulse as large as 50 to 100 mA traveling along the ground line [9]. This current pulse when introduced to lead inductances and path inductance on the PCB, could cause significant voltage spikes on the supply rails. Assuming a lead inductance of 0.1 µH (which is a fairly good representation of a 6" PCB trace) and a current spike of 20 mA with a duration of 5 ns, (for illustrative purposes, the typical values for a TTL gate are used to compute the amplitude of a possible noise

pulse.) the voltage given by V = L(dl/dt) is 0.4 V. This completely eliminates the working noise margin of TTL. Since these current spikes will only supplement each other, it is possible that with only a few gates switching (especially if their switching is synchronous), a TTL circuit could be rendered useless by its own noise. Unfortunately, since these output stages are intrinsic to the TTL gate, there is very little that could be done to eliminate this noise source. The only other viable alternative is to reduce the ground inductance as much as possible. This was done by using a combination of ground buses and ground planes wherever possible.

The second and probably the most prevalent source of noise is the MOSFET amplifiers. Their output stages suffer the same fate as the totem pole output stage of the TTL IC's since there is a period of simultaneous conduction in both gates during a transition. This rush current is extremely large since the MOSFETs have an extremely low on resistance ( $r_{DS}=0.5~\Omega$ ). This, combined with the high operating voltage of 100 V, results in massive current spikes on the ground rail. In order to eliminate the spikes caused by the amplifier, simultaneous conduction of both gates must be prevented. However, since the gates are controlled by the same input signal, it is clear that this is not a trivial task. The circuitry required to drive the high input capacitance of the power FET will also contribute to this noise since it must source and sink large currents. These considerations will be discussed further in Chapter 4.

Since it was not possible to completely eliminate the noise at the source, the mechanism of how such spikes cause an incorrect signal was analyzed so that a means of prevention could be developed. It has been already concluded that there will be large current spikes traveling along the grounds due to the switching of both the TTL gates and the amplifiers. A possible situation of how these spikes can affect the outputs is now proposed. Suppose there are 2 gates, A and B, where gate B is adjacent to a noise source. Let gate A drive gate B with an active low signal. If a current spike occurs at the noise source, it will propagate along the ground past B and towards A. Since there is a parasitic inductance in the ground line, this current spike causes a voltage spike which increases as it travels along the ground. Recall that when the output of a gate is low, the output of the NPN transistor and thus the TTL gate is saturated and is connected to ground. Thus, if a voltage spike is present on the ground of gate A, then it will appear on its logic level Since gate B is a closer reference to ground, the spike low output. on the low output of A could actually appear to B as a logic high level pulse, thus causing B to output an incorrect signal. In the UPADS this could cause an improper duty cycle or phase shift.

Several steps were taken in the attempt to minimize such current spikes. As a mandatory first step, one decoupling capacitor for every two IC's was placed as close as possible to the individual IC's on the supply rails. This form of decoupling uses capacitances as a frequency dependent impedance (where  $Z = -j/(\omega C)$ ). Since the frequency of the spikes is roughly known, the capacitor was chosen so that its impedance at this frequency is minimal. Placing these capacitors across the +5 V and ground should effectively remove any high frequency spikes. Also by liberally using these bypass capacitors on the power supply rails the effective path a spike can

travel is reduced. This lowers the inductance which in turn results in smaller voltage spikes. Furthermore, ceramic capacitors which have characteristically low inductances were used for this form of decoupling. This solution alone was sufficient to suppress the voltage spikes caused by the switching of the TTL gates. Thus, it allowed the proper operation of the DCC at low output levels of the amplifier. However, as the output of the amplifiers was increased, incorrect outputs, or glitches, began to reappear. This indicated that the spikes caused by the amplifiers when operated at high output voltages constitute the major source of noise.

There are two possible solutions to the problems due to the current spikes generated by the amplifier. The first solution involves minimizing the current spikes themselves. This was accomplished by using current limiting resistors and decoupling capacitors. Since the current spikes are due to a large rush current that flows from the high voltage rail to ground during simultaneous conduction of both MOSFETs, this current was reduced using current limiting resistors at the sources of both MOSFETs. Using 11  $\Omega$  resistor reduced the magnitude of the current spikes from 1 A to 0.434 A at an operating voltage of 10 V. Since this is still a sizeable current, two forms of decoupling were used. The first form of decoupling is identical to the one proposed above.

Since the frequency of the spikes is a known parameter ( $f_{spike}$  = 2 x  $f_{system}$ ), the decoupling capacitor was chosen such that the impedance is minimized at that frequency. The second form of decoupling utilizes capacitors as an energy storage device. The energy stored in a capacitor is given by Equation (3.2):

$$U = .5 (CV^2)$$

(3.2)

where U is the energy stored in joules, C is the capacitance in farads, and V is the voltage in volts. Since a capacitor will resist any change in voltage, it is an effective means of voltage spike suppression. For example, if a 10  $\mu F$  is presented with a current spike on the order of 100 mA over a duration of 20 ns, the effective voltage change as given by Equation (3.3):

$$\Delta V = (\Delta I \times \Delta t)/C \tag{3.3}$$

is only 0.2 V. Since this type of decoupling requires large capacitances, (evident in Equations (3.2) and (3.3)) tantalum capacitors, which have relatively large capacitances in small packages, were used for this application. The tantalum capacitors, when placed abundantly along the power buses, will act as local voltage sources, thus regulating these power supply rails.

The second solution involves minimizing the effect of these current spikes on the DCC. In order to do this, an attempt was made to prevent the spikes on the amplifier ground from reaching the DCC ground by isolating the two grounds. Unfortunately, when interfacing analog and digital circuits, a common ground is necessary as a reference in order to establish a switching threshold that is compatible with both circuits. Thus, if the digital circuits are used to switch the analog circuits, the reference is required such that the voltage outputted by the digital circuits will definitely switch the analog circuits. This may not be the case if the ground is removed and the circuits are floating with respect to each other.

The easiest and most effective means of isolating the ground is by using optoisolators. Basically, optoisolators provide an optical transmission link rather than an electrical link, thus eliminating the need for a common ground. Simple optoisolators employ lightemitting diodes as a front end and use photo-Darlington transistors to convert the optical signal to an electrical one. Because this completely eliminates any common mode noise such as ground spikes, it should definitely be used in future designs. Also, it may simplify layout and increase isolation if the amplifiers are located on a different board than the control circuits. The control circuits signal could be sent out along the bus and buffered by optoisolators placed at the input of the board.

Since incorporating optoisolators would require physically altering the PCB, the ground mecca technique was used instead. This technique utilizes individual grounds for different applications and connects them at a common point. In the UPADS, there are dedicated grounds for the digital circuits, amplifier circuits, and the chassis connected only at the main power supply. Thus, any spikes caused by the amplifiers must first travel to the power supply and then back along the digital ground in order to cause a glitch. The combination of the power supply's voltage regulators and the ground mecca's tie with earth ground is normally sufficient to dampen out any voltage spikes. This resulted in better noise immunity for the digital control circuits operating with output voltages in the vicinity of 50 V. However, even with the above modifications, there remained some occasional glitches.

The final step is to apply the understanding gained from the second step to the actual circuit. This mechanism indicates that active low inputs are most prone to noise spikes. By using a state detector at the inputs to the counter, it was determined that the glitches were due to improper presets. The inputs and outputs of the octal D-type register which buffers this data were then examined. This test showed that although the inputs received seemed to be correct, the data stored in the register was not: this implies that the data is corrupted as it enters the register. Since the noise mechanism indicates that active low inputs are susceptible to noise, the active low clock input of the 74LS374 was examined. This input is controlled by the 3 to 8 decoder which outputs an active low signal. Spikes on this signal could be interpreted as the rising edge of the load. If the spike occurs close to the falling edge, this may reduce the duration of the clock signal to an amount smaller than the valid hold time. On the other hand, if the output of the decoder is high, a negative going spike on the output from the +5 V could be interpreted as a low pulse causing the register to clock in the data intended for another amplifier. A plausible solution to this problem involves the introduction of a lowpass RC network at all of the Schmitt trigger clock inputs of the 74LS374. Since the actual signal frequency is fairly low, the 3 dB cutoff frequency was set for approximately 10 kHz. This Schmitt trigger filter effectively removes both positive and negative going spikes so that the occurrence of glitches are reduced. As a result, stable operation of the system may be achieved driving a resistive dummy load of 75  $\Omega$ . These modifications should be sufficient for the proper operation of

the system when driving the phased array applicators through matching networks. As an added insurance, the presets can be constantly refreshed using the DMA. Thus, any glitches that may occur could be corrected by the DMA during the next refresh cycle.

# CHAPTER 4 AMPLIFIER CIRCUITS

#### 4.1 Design Objective

The amplifier circuits are necessary to convert the TTL low level control signals to a level capable of driving the piezoelectric transducer elements in the array. According to the piezoelectric effect, the element's surface displacement is proportional to the voltage placed across it. Thus, in order to drive these transducers, the amplifiers should operate as a logic level controlled voltage source. Since the transducer material, lead zirconate titanate, presents a complex impedance, the amplifiers should be able to drive reactive loads. Although these elements will be matched in the final implementation, it would be useful to drive them without any matching circuits in preliminary experiments so that the actual voltages placed across the elements and the effects of the matching circuits would be known. Finally, since the system will be used to drive various phased arrays, the amplifier's power output should be large enough to drive the least efficient applicator.

## 4.2 Design Specifications

In order to implement the design objective, the amplifier circuits must have certain characteristics

Since the input to the amplifier is a signal from a NOR gate,

a gate drive circuit is required to translate the TTL level

- signal to a level which is capable of driving the MOSFETs to saturation.

- Since the large input capacitance of the power MOSFET is driven by a square wave with fast transition times, a drive circuit is required to source and sink large transient currents.

- 3. Because the amplitude information is represented by the duty cycle of the TTL signal, the output of the gate drive circuit should maintain this duty cycle.

- The amplifier should act as a voltage source capable of driving the reactive loads in the elements of the phased arrays.

- 5. The power output of the amplifier must be adjustable in order to account for the various efficiencies of different phased arrays as well as allowing the acoustical power output of a specific array to be controlled.

### 4.3 Circuit Description

The amplifier used in the UPADS switches between  $V^+=100 \text{ V}$  and  $V^-=0 \text{ V}$  as its logic level input changes. This section will compare MOSFET and bipolar transistors and analyze the amplifier used in UPADS.

## 4.3.1 Comparisons of MOSFETs and bipolar power transistors

In implementing this amplifier, there are two types of power transistors that could be used: the bipolar and the MOSFET. When

compared with power bipolar transistors, power MOSFETs offer some definite advantages. Power MOSFETs have a higher speed capability, fewer problems with thermal runaway and secondary breakdown, and a lower noise figure. However, in certain applications there are several distinct disadvantages in using power MOSFETs. Particularly, there is the problem of simultaneous conduction of both power MOSFETs in a common drain configuration.

Power MOSFETs have superior switching speeds to bipolar power transistors since they are respectively majority and minority carrier devices. Power bipolar transistors have an inherent storage time since they must remove the minority carriers stored in the base. However, since the MOSFET is a voltage controlled device, its transition time is only a function of the charge and the discharge of the gate capacitance. In turn, power MOSFETs with higher switching speeds are more efficient at higher frequencies. This is crucial for MOSFETs operating in the common drain configuration since short switching times will minimize the duration that the rush current is drawn.

The power bipolar transistors are more susceptible to thermal runaway than the MOSFETs. If the base-emitter voltage,  $V_{BE}$ , is constant, an increase in temperature causes an increase in collector current,  $I_{C}$ , which further increases the transistor's temperature. This sets up a positive feedback loop which results in thermal runaway that may eventually lead to transistor destruction.

In comparison, power MOSFETs exhibit fewer problems with thermal runaway. The drain current,  $I_D$ , of a N-channel MOSFET in saturation is given by Equation (4.1):

$$I_D = k (V_{GS} - V_T)^2$$

(4.1)

where  $V_{GS}$  is the gate-to-source voltage,  $V_T$  is the threshold voltage, and k is the conductivity parameter given by Equation (4.2):

$$k = 0.5 \,\mu_{\rm B} \,{\rm Cox} \,(W/L)$$

(4.2)

where  $\mu_n$  is the electron mobility in the induced N-channel;  $C_{OX}$  is the capacitance per unit area of the gate-to-channel capacitor with the oxide layer serving as a dielectric; W and L are respectively the width and length of the channel. According to Equation (4.1), V<sub>T</sub> with its negative temperature coefficient will cause the drain current to increase when the temperature is increased. Although the conductivity parameter k also has a negative temperature coefficient, it will cause the drain current to decrease with an increase in temperature. The magnitude of V<sub>T</sub> only decreases about 2 mV for each Celsius degree rise in temperature [10], while the temperature coefficient of k is quite large and is given by  $k \alpha c T^{-(3/2)}$ . With large drain currents, the overall effect of temperature on the drain current will be dominated by k. Thus k, with its negative temperature coefficient, will counter the increasing drain current, eliminating any possibility of thermal The on resistance of a MOSFET, r<sub>DS(on)</sub>, with its positive temperature coefficient, limits the current as the temperature increases. This will also contribute to temperature stability. Besides, the switching speed of the MOSFET, which is mostly a function of the gate capacitance, is relatively independent of The switching speed of the power bipolar transistors, temperature. on the other hand, will decrease with the increase in temperature, resulting in higher dynamic losses. Thus, it is evident that the

power MOSFETs have more favorable temperature characteristics than the bipolar transistor.

Secondary breakdown occurs because there is a nonuniform current flow across the base-emitter junction of a transistor that results in a high current density near the periphery of the junction. This increases localized power dissipation which will raise the temperature in the so-called hot spots. Since an increase in temperature causes a larger current, a form of thermal runaway, eventually ending in the destruction of the junction, will occur [11]. Fortunately, this phenomenon does not happen in power MOSFETs operated within the given ratings of the device. In addition, bipolar transistors, depending on the voltage, will require an additional margin for internal power dissipation [12]. However, this is unnecessary if the power MOSFET is operated within its safe operating area (SOA), which is solely determined by its power handling capabilities, peak current ratings, and breakdown voltage. Thus, MOSFETs allow simpler power considerations and less stringent circuit designs.

Finally, the noise figure of MOSFETs is lower than bipolar transistors. The two types of high frequency noise common to transistors are shot noise and thermal noise. Shot noise is a side effect of forward biased junctions; since MOSFETs do not possess any forward biased junctions, this is nonexistent. Thermal noise, due to moving carriers upon the flow of electrons, equally affects both transistors. Thus, the MOSFETs' total noise figure is smaller than that of the bipolar transistors. From the above comparisons, the MOSFETs are better suited for this system.

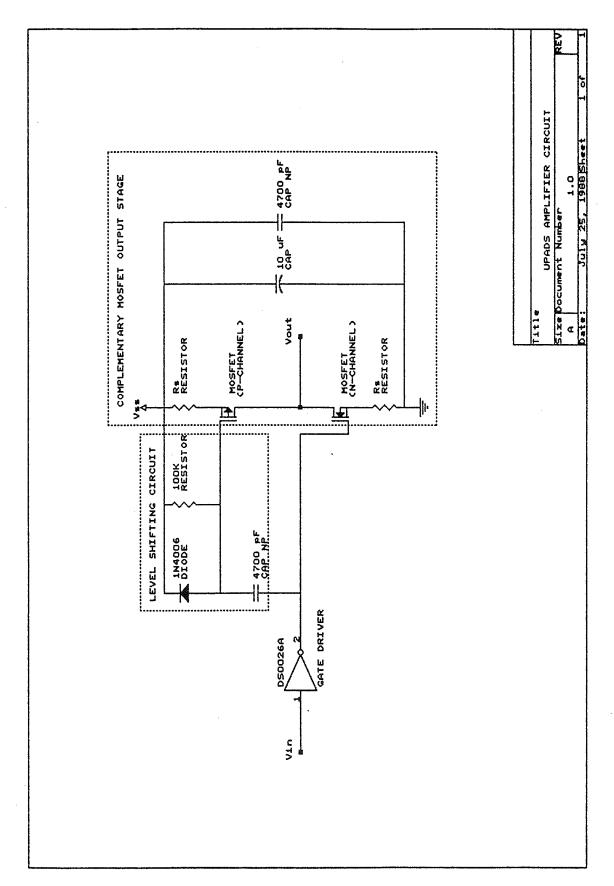

# 4.3.2 Analysis of amplifier circuit

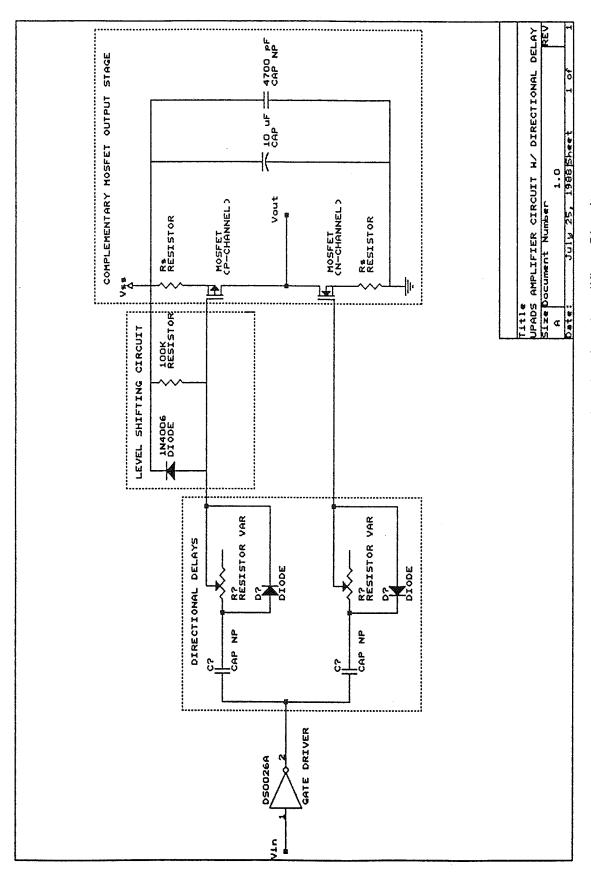

Although the components of the amplifier circuit operate in unison to produce the required output signal, for descriptive purposes, they have been classified in terms of the functions they perform: they are the gate drive circuit, the output stage circuit, and the level shifting circuit. See Figure 4.1.

#### 4.3.2.1 Gate drive circuit

Since power MOSFETs are relatively new innovations, there has been no recent developments in circuits designed specifically for MOSFET gate drive applications. However, other interface IC's can be easily adapted to serve this purpose. The integrated circuit used to implement the gate drive circuit is a DS0026 5 MHz two-phase MOS clock driver manufactured by National Semiconductor. The DS0026 possesses the desired characteristics: TTL input compatibility, high current drive, and pulse width controllability. These characteristics will now be discussed.

First, the DS0026 features TTL compatible inputs which can control an output swing of 20 V. When the input is a logic level high, the output will be connected to V<sup>-</sup>; when the input is a logic level low, the output will swing to V<sup>+</sup>. Although the DS0026 acts as an inverter, because the output stage is also an inverter, there will be no overall effect on the duty cycle of the output signal. For this system, the V<sup>+</sup> is connected to a +15 V power supply rail and the V<sup>-</sup> is attached to ground. Although the V<sub>GS</sub> threshold is +2 V and -2 V for the P-channel and the N-channel MOSFETs, respectively, the large

voltage swing ensures that both FETs will be operating in the saturation mode.

The gate driver actually determines the switching speed of the MOSFET since its current will act to charge and discharge the gate capacitance. Thus, the DS0026s high output current drive capability (up to 1.5 A) allows it to drive large capacitive loads found in power MOSFETs even while operating at extremely high speeds. For example, the DS0026 features 20 ns rise and fall times while driving a 1000 pF load with a 20 V square wave. This corresponds to a peak drive current of almost 1 A. In the amplifier circuit, with the output voltage swing set between 0 and 15 V, the gate capacitance of approximately 700 pF, and the same rise/fall times as in the above example, the circuit draws only 0.525 A. This is well within the maximum operating levels specified by the manufacturer.

Lastly, since the DS0026 was originally intended for functions such as RAM memory addressing, the output pulse width is logically controlled by the input pulse width; thus, the duty cycle information is preserved. In summary, the output of the DS0026 will be a 15 V square wave with the same duty cycle as the control signal. This output will drive the CMOS output stage, which is discussed next.

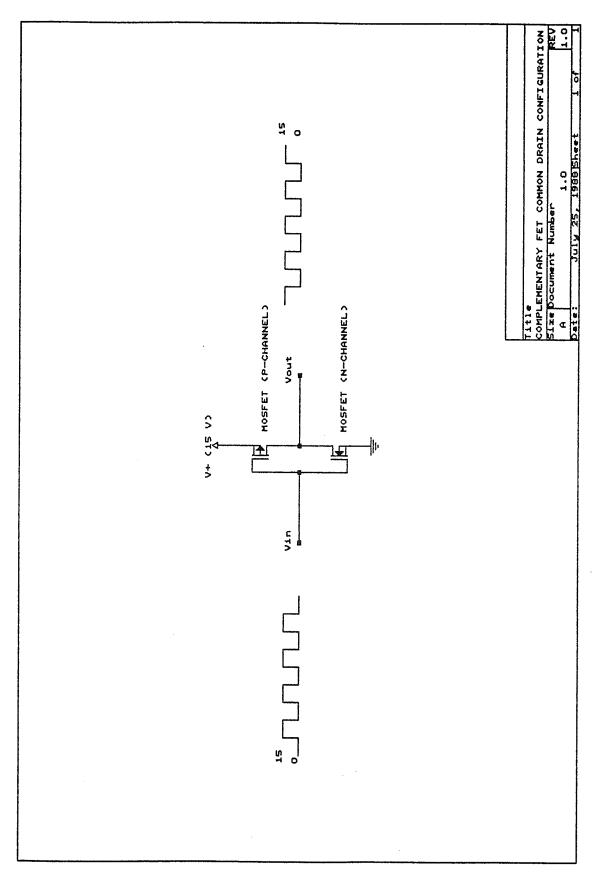

# 4.3.2.2 Output stage circuit

The output stage consists of complementary P-channel and N-channel power MOSFETs connected in a common drain configuration which specifies that the sources of the P-channel and the N-channel are tied to the high voltage supply (V+) and ground, respectively.

The gates and drains of the two MOSFETs are tied together to form the input and output, respectively See Figure 4.2. With the exception of the operating voltage, the stage's configuration and operation is almost identical to that of a CMOS inverter. As the input from the Gate Drive Circuit ( $V_{\mbox{\scriptsize IN}}$ ) increases from 0 to 15 V, the N-channel MOSFET will turn on at  $V_{\mbox{\scriptsize IN}}$  greater than or equal to  $V_{GSN(th)}$  (where  $V_{GSN(th)}$  is the gate-to-source threshold voltage for the N-channel MOSFET) and the P-channel MOSFET will turn off at  $(V_{SS}$  -  $V_{IN})$  less than or equal to  $|V_{SGP(th)}|$  (where  $V_{SGP(th)}$  is the source-to-gate threshold voltage for the P-channel MOSFET) causing the output to go low. The output will remain low and will pull current from the load until the input decreases from 15 to 0 V. The P-channel turns on at  $(V_{SS} - V_{IN}) >= |V_{SGP(th)}|$  and the N-channel to turn off at  $V_{IN} \leftarrow V_{GSN(th)}$ , forcing the output high and pushing current into the load. Therefore, the stage acts as a complementary push-pull amplifier.

Note also that the output stage merely switches the load between the V<sup>+</sup> and ground as dictated by its input. This switching mode configuration offers several advantages

1. When the load is switched to  $V_{SS}$ , it virtually sees an ideal voltage source since the MOSFETs output impedance is only  $0.4~\Omega$ . This gives the amplifier a high driving current capability since the load can sink as much current as the power supply can deliver (within the maximum drain current limitations of the MOSFET). Upon switching to ground, the load will have a low impedance path to ground, allowing any of its remaining energy to be dissipated through the ground.

- 2. Although an NMOS switch has short fall times but long rise times, the symmetry of the circuit offers fast rise and fall times. The fast speed is a result of the simultaneous action of the MOSFETs; as the P-channel MOSFET is turning off, the N-Channel MOSFET turns on and vice versa. This, however, presents a problem during periods when both MOSFETs are on. It will be covered more thoroughly in the next section.

- 3. This configuration is useful when driving inductive loads such as a stray or lead inductance, since it utilizes the intrinsic Drain-Source (D-S) diodes as free-wheeling diodes. The main consideration when driving inductive loads is the voltage transients caused by breaking the flow of current through the inductor. For example, if the Pchannel MOSFET has been turned on such that a current has been established from the power supply rail to ground, then the switching of the load to ground will cause this current to be interrupted. However, according to V = L(dI/dt), an instantaneous change in current requires an infinite voltage across the inductance. Since this is simply not possible, the voltage across the inductance abruptly increases and continues to do so until it can drive a current through the inductance. This voltage normally tends to exceed the breakdown voltage limits of the MOSFET, causing permanent damage to the device. However, this can be prevented by using the MOSFETs in the common drain configuration. If the N-channel MOSFET is on, then a load current will flow through it from the inductance to the ground; however,

when the N-channel MOSFET turns off, the current's path to ground will be blocked. Instead of causing a voltage transient, the current will flow through the P-channel's D-S diode into the positive supply rail. This diode channels the current away from the MOSFETs and clamps the flyback voltage to V<sup>+</sup> so that the complementary MOSFET is protected from the flyback voltage breakdown. It is readily apparent that this will also hold when the P-channel is initially conducting. The effectiveness of this means of suppression is contingent on whether the D-S diode can quickly and adequately clamp the flyback voltage. Since the diode has a comparable maximum current rating and switching speed with respect to its power MOSFET, it is normally adequate. However, should the need arise, a fast switching diode such as a Schottky diode could be placed in parallel with the D-S diode to shunt any excess current and protect the integral D-S diode.

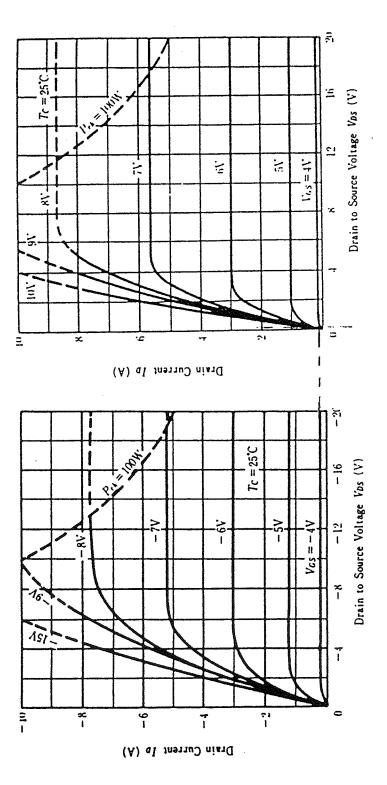

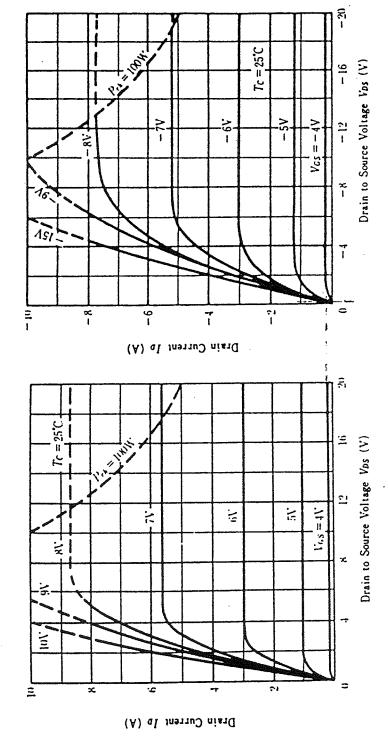

4. This configuration draws very little quiescent current for both levels of input. The operating point of the output stage can be determined for either state of the input. For a high input, the operating point is simply the intersection of the I<sub>D</sub>-V<sub>DS</sub> characteristic curve for the N-channel MOSFET at V<sub>GSN</sub> = 15 V and the I<sub>D</sub>-V<sub>SD</sub> curve for the P-channel when V<sub>SGP</sub> = 0 V. To illustrate this, the characteristic curves of the two MOSFETs are shown in Figure 4.3. The intersection of the curves indicates the operating point. Although this is a qualitative estimate (since the V<sub>GSN</sub> = 15 V curve and the

V<sub>SGP</sub> = 0 V curve are not shown), it serves its purpose in representing how little current the MOSFETs will draw while still maintaining the required low output. The actual current will be lower since the curves' intersection and operating point will all be lower. For a low input, the operating point is given by the intersection of the ID-VDS characteristic curve for the N-channel MOSFET at a V<sub>GSN</sub> = 0 V and the ID-VSD curve for a P-channel MOSFET with VSGP = 15 V. According to the curves, given in Figure 4.4, the operating point will be at VDD, still requiring very little quiescent current. Thus, the transient current dissipation is extremely small in both states. Note that this analysis will only hold if VSGP is kept at 15 V. Therefore, if the Pchannel MOSFET is operated at levels higher than 15 V, it becomes necessary to shift the gate's input voltage such that this relationship is maintained.

# 4.3.2.3 Level shifting circuit

The level shifting circuit allows the 0 to 15 V signal from the gate drive circuit to deactivate the P-channel power MOSFET. Since the P-channel source with a threshold voltage of  $V_{SG(th)} = -2$  V is tied to  $V_{CC}$  through a source resistor,  $R_S$ , the P-channel FET will not turn off until

$$V_{SG} < V_{CC} - I_D R_S - 2 \tag{4.3}$$

where  $V_{SG}$  is the gate to source voltage, and  $I_D$  is the drain current. If  $I_D$  is assumed to be 0.2 A (the nominal current drawn by an amplifier when driving a transducer element in the Sector Vortex

Array with  $R_S = 10 \Omega$  and  $V_{CC} = 100 V$ ), then the P-channel will remain activated until V<sub>SG</sub> = 96 V or less. However, the maximum that the gate drive circuit will output is only 15 V, and thus the P-Channel FET will remain on continuously. In actuality, since the maximum VSG that the P-channel MOSFET can withstand is only 20 V, the P-channel FET would probably experience a source-to-gate In order to avoid this, the level shifting circuit elevates the output of the gate drive circuit to roughly V<sub>CC</sub> - 15 V and feeds this into the P-channel FET. The output is elevated by setting the steady state voltage at the gate of the P-channel to be  $V_{CC}$  through a large pull-up resistor (R = 100K $\Omega$ ). In the absence of an input signal, there is no path for any current to flow; thus the resistor allows V<sub>SG</sub> to settle at V<sub>CC</sub>. The gate drive signal is then ac coupled into the gate voltage via a 4700 pF capacitor that presents a relatively low impedance to signals with frequencies as low as 500 kHz. This will effectively block the steady state voltage of the P-channel from reaching the N- channel. When the gate drive signal goes high, the ac coupled P-channel gate signal would swing to 115 V. However, this would limit the negative swing of the ac coupled signal to 100 V, which is insufficient to switch the Pchannel FET. Thus, a clamping diode, in parallel with the pull-up resistor, is used to limit the maximum gate signal to 100.7 V (There is a 0.7 V drop to forward bias the diode.) Therefore, when the gate drive signal goes low, the ac coupled signal will drop to 85.7 V. This will cause the P-channel FET to go into the saturation mode without exposing it to voltages exceeding its gate to source

breakdown. Thus, the level shifting circuit offsets the ac coupled signal by 85.7 V in order to regulate the P-channel FET.

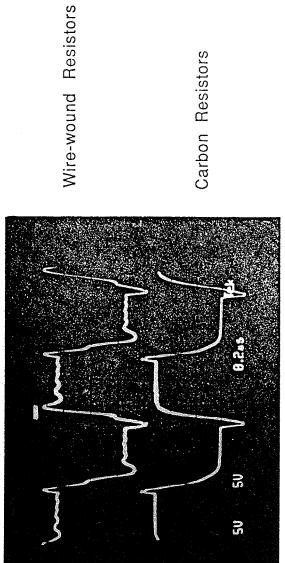

#### 4.4 Hardware

Although the Hitachi 2-SK400 N-channel MOSFET and a 2-SJ114 P-channel MOSFET were used in initial amplifier prototypes, they subsequently were replaced by a Samsung IRFP-9230 P-channel MOSFET and a IRFP-230 N-channel MOSFET. The Samsung MOSFETs offer comparable performance at considerable cost reduction. For example, both the IRFP-9230 and the IRFP-230 have a maximum operating voltage of 200 V and a maximum drain current of 9 A. If they are used to drive a 50  $\Omega$  resistive load, the output power would be on the order of 800 W, which exceeds by far the nominal power needed to drive an individual element. The MOSFETs are operated below the maximum voltage to allow a margin for transients while still providing a large power output. Ceramic capacitors with their relatively low inductance were used for the 4700 pF capacitors; electrolytic capacitors with their small size were for the 10 μF capacitors. The diode is a rectifier diode with fast switching speed and large current capability. Molded carbon resistors were used for the pull up and source resistors because of their relatively low inductance even at high frequencies. Although wire wound resistors offer higher power handling capabilities, their use is prohibited by their high inductances. Minimizing inductance is important because it can cause voltage spikes when presented with current spikes. These spikes will be largest during periods of simultaneous conduction. Also, resonant circuits, set up by inductances and

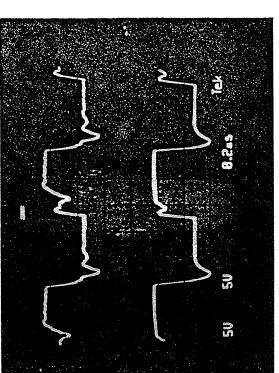

parasitic capacitances can cause ringing in the power supply rails and the grounds. Figure 4.5 shows the ringing at the amplifier output when the same size wire wound resistors and carbon resistors are used as the source resistors. This ringing can couple into the output of the gate drive through the ground and power supply rails. In turn, ringing on the gate drive output can couple across the input capacitance of the MOSFET to further increase the ringing of the amplifier output signal. (Recall that the amplifier, operating in the saturation mode, only responds to the logic state of the input signal. Thus, the only way that small input noise signal can pass through the MOSFET to the output is via capacitive coupling. Because the input gate capacitance is quite large and the noise frequency is high, capacitive coupling will be prominent.) Figure 4.6 shows the additional ringing present on the gate drive signal and contrasts it to the gate drive signal of the configuration utilizing the carbon resistors. This ringing should be avoided at all costs because it will degrade the output signal. Furthermore, MOSFET failure can occur if the ringing causes the output signal to exceed the maximum gate to source voltage. Thus, the carbon resistors were used in lieu of their lower power handling abilities. The amount of power dissipated in Rs however can be increased by paralleling these carbon resistors.

## 4.5 Practical Considerations and Future Recommendations

The only major shortcoming in this design is a problem that is inherent in all CMOS inverters: the simultaneous conduction of both MOSFETs that occurs during input transitions. The positive

transition causes the N-channel MOSFET to be turned on before the P-channel MOSFET is turned off; negative transition causes the P-channel MOSFET to be turned on before the N-channel MOSFET is turned off. The duration that both MOSFETs remain on during the positive transition is a function of the input waveform rise time as well as the N-channel turn-on time, T<sub>NON</sub>, and the P-channel turn-off time, T<sub>POFF</sub>. Let T<sub>PVGS(th)</sub> denote the time it takes the input to achieve the turn-on potential for the N-channel MOSFET and T<sub>PVSG(th)</sub> denote the time it takes the input to reach the turn-off threshold for the P-channel MOSFET then the duration of simultaneous conduction during the positive transition, T<sub>SCP</sub>, is given by Equation (4.4):

$T_{SCP} = (T_{POFF} + T_{PVSG(th)}) - (T_{NON} + T_{PVGS(th)}) \quad (4.4)$  The period that both MOSFETs conduct during the negative transition of the input wave is dependent on its fall time in addition to the P-channel turn-on time,  $T_{PON}$ , and the N-channel turn-off time,  $T_{NOFF}$ . If  $T_{NVSG(th)}$  represents the time required for the input to fall to the turn on threshold for the P-channel MOSFET and  $T_{NVGS(th)}$  represents the time it takes for the input to realize the turn-off potential for the N-channel MOSFET then the period of simultaneous conduction during the negative transition,  $T_{SCN}$ , is given by Equation (4.5):

$T_{SCN} = (T_{NOFF} + T_{NVGS(th)}) - (T_{PON} + T_{NVSG(th)})$  (4.5)

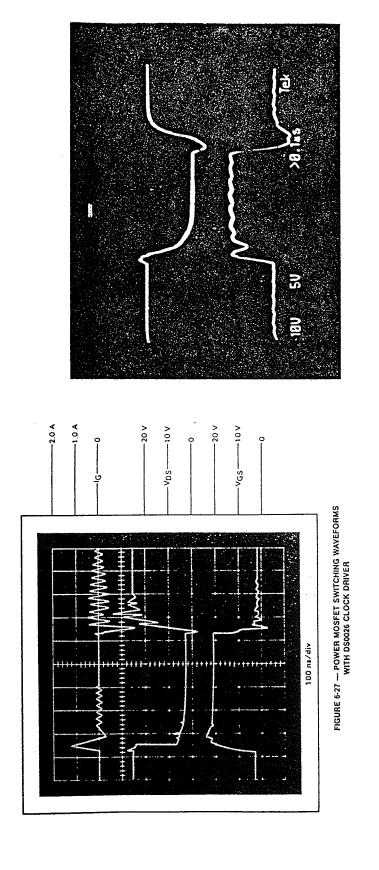

Using the rise and fall times of the gate driver (DS0026) output, T<sub>NVGS(th)</sub>, T<sub>NVSG(th)</sub>, T<sub>PVGS(th)</sub>, and T<sub>PVSG(th)</sub> can be calculated. The values for T<sub>NON</sub>, T<sub>NOFF</sub>, T<sub>PON</sub>, and T<sub>POFF</sub> are given in the data sheets for the N-channel MOSFET (IRFP-230) and the P-channel MOSFET (IRFP-9230). Using these values, T<sub>SCP</sub> and T<sub>SCN</sub> were calculated to be approximately 98 ns and 33 ns, respectively. Thus,

the MOSFETs will both be conducting for a total of 131 ns during one period of the output. At a frequency of 700 kHz, 18% of the output period is spent in the simultaneous conduction mode, during which most of the current drains into the ground, causing a significant power loss. Moreover, the high currents associated with this mode cause substantial noise problems (as was mentioned in Chapter 3) and possibly MOSFET damages.

There are two viable methods for dealing with simultaneous conduction: utilizing current-limiting resistors to minimize the magnitude of the rush current (discussed in Chapter 3) and introducing a delay to the gate inputs to directly prevent the simultaneous conduction. It is evident from Equation (4.4) that TSCP can be reduced to zero if the rightmost sum is increased by TD so that the two sums are equal. Although T<sub>NON</sub> is fixed, it is possible to increase TpvGS(th) by introducing a delay with a time constant equal to Tp to the input of the N-channel. A simple RC circuit with time constant,  $\tau = T_D$ , can be implemented using the input capacitance of the MOSFET and an external resistor. According to the N-channel MOSFETs data sheets, the input capacitance, CISS, is 800 pF. Thus, if a 122  $\Omega$  resistor is placed in series with the gate input, the input waveform will be delayed by 98 ns causing the Nchannel MOSFET to switch on at the same instant as the P-channel is switched off. A slightly larger resistor should be used to ensure asynchronous switching by the MOSFETs. Unfortunately, the external resistor will also delay the N-channel from turning off, thus defeating its purpose. This can be overcome by inserting a diode in parallel with the resistor. See Figure 4.7. This will make the delays unidirectional; the deactivation of the N-channel will not be delayed since the charge stored in the gate capacitance will flow through the diode rather than the resistor [13]. The same approach can be used to delay the P-channel from turning on before the N-channel turns off on the negative transition. Since this approach involves physically altering the PCB, the first method was used. However, it should be definitely utilized in any future designs.

A general consideration intrinsic to this amplifier and CMOS is that the inputs must never be left floating. This will raise the output of the amplifier to V<sup>+</sup>/2, which will force both MOSFETs into saturation. The resulting rush current will eventually cause the MOSFETs to fail. Thus, provisions must be made such that the amplifier is always referenced to an input.

Specifically, some problems that are normally associated with this type of complementary push-pull amplifier have been accounted for in this design. First, protection against silicon controlled rectifier (SCR) latch-up has been incorporated in the circuit. This occurs when the input exceeds the V<sup>+</sup> of the amplifier, causing the input protection diode of the P-channel to be forward biased. The large current that flows through the diode causes the MOSFET to increase in temperature and latch-up so that correct operation can only be restored by turning off the power source for the amplifier. Should this current continue to flow through the diode, it will eventually lead to the destruction of the MOSFET. A preliminary inspection of the circuit indicates that this cannot occur in the amplifier circuit used in UPADS. The 4700 pF capacitor at the input of the P-channel MOSFET will block any dc input voltage from

reaching the gate of the P-channel and prevent SCR latch-up. Even if a transient or spike does pass through the capacitor, the clamping diode will kick in and help dissipate the current into V<sup>+</sup>.

In the past, short circuits at the output often caused by faulty cables connecting the array to the matching circuit were the major cause of MOSFET failure. Thus, short-circuit protection has been implemented by setting source resistance, Rs, such that the maximum current pulled through the MOSFET is below the maximum allowable drain current even at the maximum operating voltage.

Although this does result in an increased power loss in Rs, amplifier reliability was gained. If a short-circuited output occurs in the present system, Rs should be able to withstand the additional power dissipation for a short duration to allow the operator to shut down the system. In the event of resistor failure, since the impedance normally becomes quite large, the MOSFET will be protected. Thus, the only repair necessary will be that of the source resistors, which are relatively inexpensive.

The circuit layout emphasized minimizing path inductances. For example, the path between the gate drive circuit and the input of the MOSFET gate was minimized and made as wide as possible. Power supply buses were also implemented in this fashion and ground planes were used wherever the circuit layout allowed.

From the noise problems considered in Chapter 3, it is obvious that the power and ground buses could still use some improvement. For example, potential differences of almost 2 V were found on different locations of the high voltage ground due to the inductance and large current transients present on the bus. Connecting this bus

to a ground plane in various locations by ground straps minimized this difference in potentials. In future designs, multilayered boards with layers dedicated to power distribution and grounding should be used. If this is not feasible, power distribution should be designed as a tree network so that a main power supply trunk branches to various areas of the PCB to minimize voltage potential differences on the bus.

Lastly, a form of output feedback is present in the circuit. As the drain current flows through R<sub>S</sub>, a voltage drop proportional to this current occurs in series with the output voltage. In the event of large drain currents, this voltage drop will reduce the effective voltage between the gate and the source in the P-channel. Recall that as V<sub>SGP</sub> is decreased, the MOSFET will come out of the saturation mode so that the drain current will subsequently decrease. Therefore, this negative feedback protects the MOSFET by shutting it down when large drain current is present.

Future modifications should include gate protection which can be implemented using a varistor or zener diode. For example, a 15 V zener diode placed across the gate-to-source inputs of both MOSFETs will prevent any input transients from causing a gate-to-source breakdown. Also, placing a resistor-capacitor (RC) snubber across the drain-to-source outputs will help to reduce any remaining ringing present at the outputs.

The culmination of these modifications and the decision to use the power MOSFETs as the output stage have led to an amplifier with many desirable characteristics: high resistance to electrical failure, minimal drive requirements, high operating temperature, fast

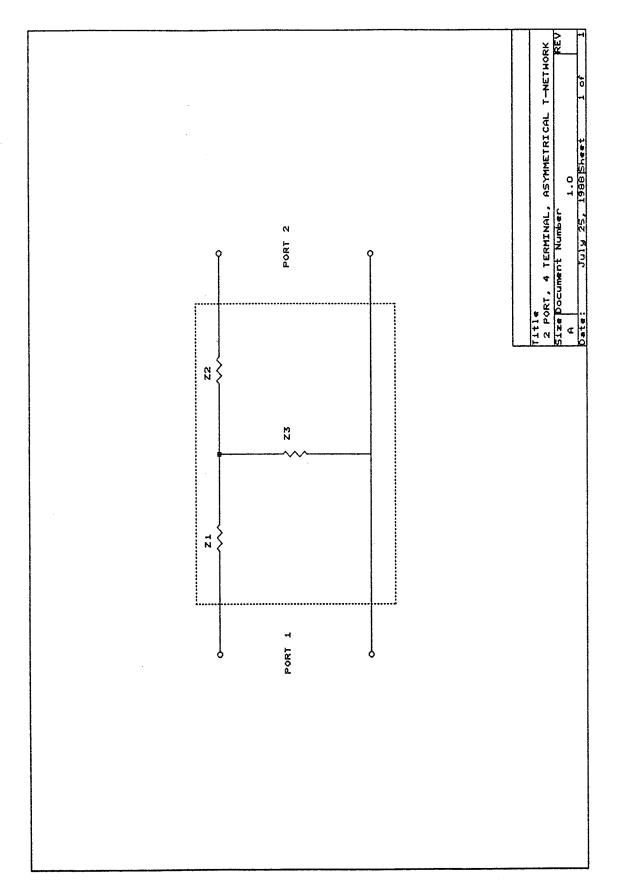

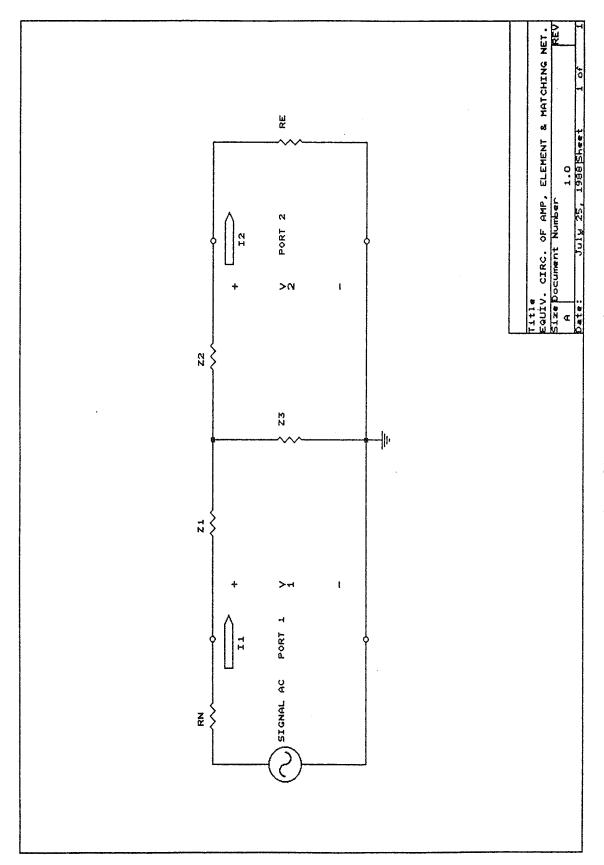

switching speeds, and a high power output capable of driving reactive loads. Through the combination of proper circuit layout, adequate decoupling, component selection, and effective modifications, this amplifier has a response that is comparable to commercial amplifiers. For comparison, the response of an amplifier taken from a Motorola data book is displayed in Figure 4.8. The MOSFET used in this amplifier has a comparable input capacitance, maximum operating voltage, and maximum drive current to the ones used in the UPADS' amplifier. Also, the gate drive used in this circuit is identical to the one used in the amplifier circuit. Figure 4.9 displays the response of the UPADS' amplifier operating at the same output levels utilizing identical inputs. The UPADS' amplifier output compares guite favorably to that of the Motorola amplifier. In conclusion, this amplifier should prove to be durable as well as capable of driving the loads presented by the phased array applicators.